2024-11-25 07:08:48

在芯片設(shè)計(jì)領(lǐng)域,知識(shí)產(chǎn)權(quán)保護(hù)是維護(hù)創(chuàng)新成果和確保企業(yè)競(jìng)爭(zhēng)力的關(guān)鍵。設(shè)計(jì)師在創(chuàng)作過(guò)程中不僅要避免侵犯他人的權(quán),以免引起法律糾紛和經(jīng)濟(jì)損失,同時(shí)也需要積極為自己的創(chuàng)新成果申請(qǐng),確保其得到法律的保護(hù)。 避免侵犯他人的首要步驟是進(jìn)行的檢索和分析。設(shè)計(jì)師在開始設(shè)計(jì)之前,需要對(duì)現(xiàn)有技術(shù)進(jìn)行徹底的調(diào)查,了解行業(yè)內(nèi)已有的布局,確保設(shè)計(jì)方案不與現(xiàn)有發(fā)生。這通常需要專業(yè)的知識(shí)產(chǎn)權(quán)律師或代理人的協(xié)助,他們能夠提供專業(yè)的搜索服務(wù)和法律意見。 在確保設(shè)計(jì)不侵權(quán)的同時(shí),設(shè)計(jì)師還需要為自己的創(chuàng)新點(diǎn)積極申請(qǐng)。申請(qǐng)是一個(gè)復(fù)雜的過(guò)程,包括確定發(fā)明的新穎性、創(chuàng)造性和實(shí)用性,準(zhǔn)備詳細(xì)的技術(shù)文檔,以及填寫申請(qǐng)表格。設(shè)計(jì)師需要與律師緊密合作,確保申請(qǐng)文件的質(zhì)量和完整性。精細(xì)化的芯片數(shù)字木塊物理布局,旨在限度地提升芯片的性能表現(xiàn)和可靠性。浙江射頻芯片數(shù)字模塊物理布局

芯片設(shè)計(jì)的流程是一項(xiàng)精細(xì)且系統(tǒng)化的工作,它從規(guī)格定義這一基礎(chǔ)步驟開始,確立了芯片所需達(dá)成的功能和性能目標(biāo)。這一階段要求設(shè)計(jì)團(tuán)隊(duì)深入理解市場(chǎng)需求、技術(shù)趨勢(shì)以及潛在用戶的期望,從而制定出一套的技術(shù)規(guī)格說(shuō)明書。 隨后,架構(gòu)設(shè)計(jì)階段接踵而至,這是構(gòu)建芯片概念框架的關(guān)鍵時(shí)期。設(shè)計(jì)師們需要決定芯片的高層結(jié)構(gòu),包括處理、存儲(chǔ)解決方案、輸入/輸出端口以及其他關(guān)鍵組件,并規(guī)劃它們之間的交互方式。架構(gòu)設(shè)計(jì)直接影響到芯片的性能和效率,因此需要精心策劃和深思熟慮。 邏輯設(shè)計(jì)階段緊隨其后,這一階段要求設(shè)計(jì)師們將架構(gòu)設(shè)計(jì)轉(zhuǎn)化為具體的邏輯電路,使用硬件描述語(yǔ)言來(lái)描述電路的行為。邏輯設(shè)計(jì)的成功與否,決定了電路能否按照預(yù)期的方式正確執(zhí)行操作。江蘇ic芯片設(shè)計(jì)流程芯片數(shù)字模塊物理布局的自動(dòng)化工具能夠提升設(shè)計(jì)效率,減少人工誤差。

芯片,這個(gè)現(xiàn)代電子設(shè)備不可或缺的心臟,其起源可以追溯到20世紀(jì)50年代。在那個(gè)時(shí)代,電子設(shè)備還依賴于體積龐大、效率低下的真空管來(lái)處理信號(hào)。然而,隨著科技的飛速發(fā)展,集成電路的誕生標(biāo)志著電子工程領(lǐng)域的一次。這種集成度極高的技術(shù),使得電子設(shè)備得以實(shí)現(xiàn)前所未有的小型化和高效化。 從初的硅基芯片,到如今應(yīng)用于個(gè)人電腦、智能手機(jī)和服務(wù)器的微處理器,芯片技術(shù)的每一次突破都極大地推動(dòng)了信息技術(shù)的進(jìn)步。微處理器的出現(xiàn),不僅極大地提升了計(jì)算速度,也使得復(fù)雜的數(shù)據(jù)處理和存儲(chǔ)成為可能。隨著工藝的不斷進(jìn)步,芯片的晶體管尺寸從微米級(jí)縮小到納米級(jí),集成度的提高帶來(lái)了性能的飛躍和功耗的降低。 此外,芯片技術(shù)的發(fā)展也催生了新的應(yīng)用領(lǐng)域,如人工智能、物聯(lián)網(wǎng)、自動(dòng)駕駛等。這些領(lǐng)域?qū)π酒男阅芎涂煽啃蕴岢隽烁叩囊蟆榱藵M足這些需求,芯片制造商不斷探索新的材料、設(shè)計(jì)和制造工藝。例如,通過(guò)使用的光刻技術(shù)和3D集成技術(shù),芯片的性能和功能得到了進(jìn)一步的擴(kuò)展。

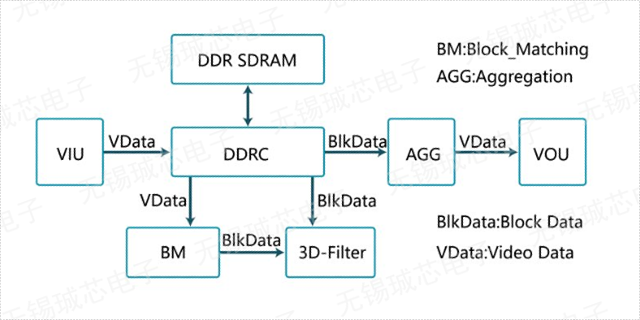

芯片的電路設(shè)計(jì)階段進(jìn)一步細(xì)化了邏輯設(shè)計(jì),將邏輯門和電路元件轉(zhuǎn)化為可以在硅片上實(shí)現(xiàn)的具體電路。這一階段需要考慮電路的精確實(shí)現(xiàn),包括晶體管的尺寸、電路的布局以及它們之間的連接方式。 物理設(shè)計(jì)是將電路設(shè)計(jì)轉(zhuǎn)化為可以在硅晶圓上制造的物理版圖的過(guò)程。這包括布局布線、功率和地線的分配、信號(hào)完整性和電磁兼容性的考慮。物理設(shè)計(jì)對(duì)芯片的性能、可靠性和制造成本有著直接的影響。 驗(yàn)證和測(cè)試是設(shè)計(jì)流程的后階段,也是確保設(shè)計(jì)滿足所有規(guī)格要求的關(guān)鍵環(huán)節(jié)。這包括功能驗(yàn)證、時(shí)序驗(yàn)證、功耗驗(yàn)證等,使用各種仿真工具和測(cè)試平臺(tái)來(lái)模擬芯片在各種工作條件下的行為,確保設(shè)計(jì)沒有缺陷。 在整個(gè)設(shè)計(jì)流程中,每個(gè)階段都需要嚴(yán)格的審查和反復(fù)的迭代。這是因?yàn)樾酒O(shè)計(jì)的復(fù)雜性要求每一個(gè)環(huán)節(jié)都不能有差錯(cuò),任何小的疏忽都可能導(dǎo)致終產(chǎn)品的性能不達(dá)標(biāo)或無(wú)法滿足成本效益。設(shè)計(jì)師們必須不斷地回顧和優(yōu)化設(shè)計(jì),以應(yīng)對(duì)技術(shù)要求和市場(chǎng)壓力的不斷變化。完整的芯片設(shè)計(jì)流程包含前端設(shè)計(jì)、后端設(shè)計(jì)以及晶圓制造和封裝測(cè)試環(huán)節(jié)。

詳細(xì)設(shè)計(jì)階段是芯片設(shè)計(jì)過(guò)程中關(guān)鍵的部分。在這個(gè)階段,設(shè)計(jì)師們將對(duì)初步設(shè)計(jì)進(jìn)行細(xì)化,包括邏輯綜合、布局和布線等步驟。邏輯綜合是將HDL代碼轉(zhuǎn)換成門級(jí)或更低層次的電路表示,這一過(guò)程需要考慮優(yōu)化算法以減少芯片面積和提高性能。布局和布線是將邏輯綜合后的電路映射到實(shí)際的物理位置,這一步驟需要考慮電氣特性和物理約束,如信號(hào)完整性、電磁兼容性和熱管理等。設(shè)計(jì)師們會(huì)使用專業(yè)的電子設(shè)計(jì)自動(dòng)化(EDA)工具來(lái)輔助這一過(guò)程,確保設(shè)計(jì)滿足制造工藝的要求。此外,詳細(xì)設(shè)計(jì)階段還包括對(duì)電源管理和時(shí)鐘樹的優(yōu)化,以確保芯片在不同工作條件下都能穩(wěn)定運(yùn)行。設(shè)計(jì)師們還需要考慮芯片的測(cè)試和調(diào)試策略,以便在生產(chǎn)過(guò)程中及時(shí)發(fā)現(xiàn)并解決問(wèn)題。芯片設(shè)計(jì)過(guò)程中,架構(gòu)師需要合理規(guī)劃資源分配,提高整體系統(tǒng)的效能比。浙江數(shù)字芯片設(shè)計(jì)流程

芯片前端設(shè)計(jì)階段的高層次綜合,將高級(jí)語(yǔ)言轉(zhuǎn)化為具體電路結(jié)構(gòu)。浙江射頻芯片數(shù)字模塊物理布局

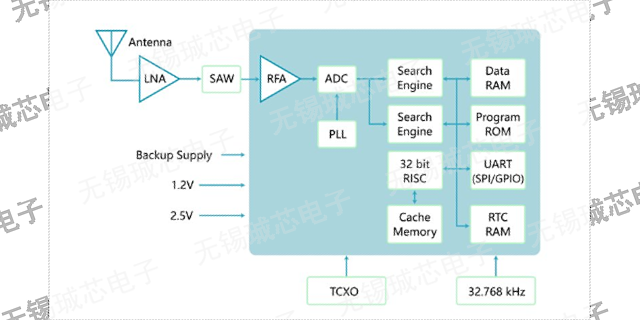

傳感器芯片是另一種重要的芯片類型,它們?cè)诟鞣N檢測(cè)和測(cè)量設(shè)備中發(fā)揮著關(guān)鍵作用。傳感器芯片能夠?qū)⑽锢砹浚ㄈ鐪囟取毫Α⒐饩€等)轉(zhuǎn)換為電信號(hào),為自動(dòng)化控制系統(tǒng)提供必要的輸入。隨著物聯(lián)網(wǎng)(IoT)的興起,傳感器芯片的應(yīng)用范圍越來(lái)越,從智能家居到工業(yè)自動(dòng)化,再到環(huán)境監(jiān)測(cè),它們都是不可或缺的組成部分。 通信芯片則負(fù)責(zé)處理數(shù)據(jù)傳輸和通信任務(wù)。它們?cè)跓o(wú)線網(wǎng)絡(luò)、移動(dòng)通信、衛(wèi)星通信等領(lǐng)域扮演著重要角色。隨著5G技術(shù)的推廣和應(yīng)用,通信芯片的性能和功能也在不斷提升,以支持更高的數(shù)據(jù)傳輸速率和更復(fù)雜的通信協(xié)議。浙江射頻芯片數(shù)字模塊物理布局