2024-11-27 08:09:04

為了進一步提高測試的覆蓋率和準確性,設計師還會采用仿真技術,在設計階段對芯片進行虛擬測試。通過模擬芯片在各種工作條件下的行為,可以在實際制造之前發現潛在的問題。 在設計可測試性時,設計師還需要考慮到測試的經濟性。通過優化測試策略和減少所需的測試時間,可以降低測試成本,提高產品的市場競爭力。 隨著芯片設計的復雜性不斷增加,可測試性設計也變得越來越具有挑戰性。設計師需要不斷更新他們的知識和技能,以應對新的測試需求和技術。同時,他們還需要與測試工程師緊密合作,確保設計滿足實際測試的需求。 總之,可測試性是芯片設計中不可或缺的一部分,它對確保芯片的質量和可靠性起著至關重要的作用。通過在設計階段就考慮測試需求,并采用的測試技術和策略,設計師可以提高測試的效率和效果,從而為市場提供高質量的芯片產品。芯片架構設計決定了芯片的基本功能模塊及其交互方式,對整體性能起關鍵作用。北京網絡芯片后端設計

在芯片設計領域,知識產權保護是維護創新成果和確保企業競爭力的關鍵。設計師在創作過程中不僅要避免侵犯他人的權,以免引起法律糾紛和經濟損失,同時也需要積極為自己的創新成果申請,確保其得到法律的保護。 避免侵犯他人的首要步驟是進行的檢索和分析。設計師在開始設計之前,需要對現有技術進行徹底的調查,了解行業內已有的布局,確保設計方案不與現有發生。這通常需要專業的知識產權律師或代理人的協助,他們能夠提供專業的搜索服務和法律意見。 在確保設計不侵權的同時,設計師還需要為自己的創新點積極申請。申請是一個復雜的過程,包括確定發明的新穎性、創造性和實用性,準備詳細的技術文檔,以及填寫申請表格。設計師需要與律師緊密合作,確保申請文件的質量和完整性。北京AI芯片工藝IC芯片,即集成電路芯片,集成大量微型電子元件,大幅提升了電子設備的性能和集成度。

除了硬件加密和**啟動,設計師們還采用了多種其他**措施。例如,**存儲區域可以用來存儲密鑰、證書和其他敏感數據,這些區域通常具有防篡改的特性。訪問控制機制可以限制對關鍵資源的訪問,確保只有授權的用戶或進程能夠執行特定的操作。 隨著技術的發展,新的**威脅不斷出現,設計師們需要不斷更新**策略和機制。例如,為了防止側信道攻擊,設計師們可能會采用頻率隨機化、功耗屏蔽等技術。為了防止物理攻擊,如芯片反向工程,可能需要采用防篡改的封裝技術和物理不可克隆函數(PUF)等。 此外,**性設計還涉及到整個系統的**性,包括軟件、操作系統和應用程序。芯片設計師需要與軟件工程師、系統架構師緊密合作,共同構建一個多層次的**防護體系。 在設計過程中,**性不應以性能和功耗為代價。設計師們需要在保證**性的同時,也考慮到芯片的性能和能效。這可能需要采用一些創新的設計方法,如使用同態加密算法來實現數據的隱私保護,同時保持數據處理的效率。

隨著全球對環境保護和可持續發展的重視,芯片設計領域也開始將環境影響作為一個重要的考量因素。設計師們正面臨著在不性能的前提下,減少芯片對環境的影響,特別是降低能耗和碳足跡的挑戰。 在設計中,能效比已成為衡量芯片性能的關鍵指標之一。高能效的芯片不僅能夠延長設備的使用時間,減少能源消耗,同時也能夠降低整個產品生命周期內的碳排放。設計師們通過采用的低功耗設計技術,如動態電壓頻率調整(DVFS)、電源門控、以及睡眠模式等,來降低芯片在運行時的能耗。 此外,材料的選擇也是減少環境影響的關鍵。設計師們正在探索使用環境友好型材料,這些材料不僅對環境的影響較小,而且在能效方面也具有優勢。例如,采用新型半導體材料、改進的絕緣材料和的封裝技術,可以在提高性能的同時,減少生產過程中的能源消耗和廢棄物的產生。芯片后端設計涉及版圖規劃,決定芯片制造過程中的光刻掩模版制作。

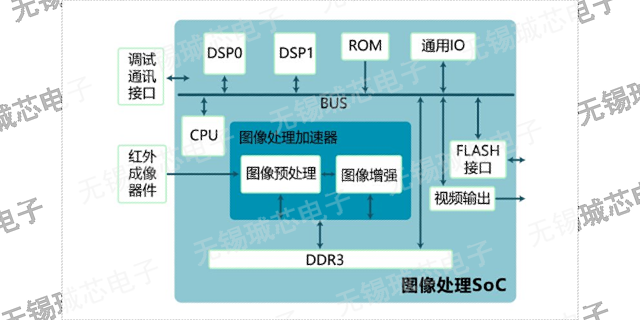

芯片的電路設計階段進一步深化了邏輯設計,將邏輯門和電路元件轉化為可以在硅片上實現的具體電路。設計師們需要考慮晶體管的尺寸、電路的布局以及它們之間的連接方式,同時還要考慮到工藝的可行性和成本效益。 物理設計是將電路設計轉化為可以在硅晶圓上制造的物理版圖的過程。這一階段包括布局布線、功率和地線的分配、信號完整性和電磁兼容性的考慮。物理設計對芯片的性能、可靠性和制造成本有著直接的影響。 驗證和測試是設計流程的后階段,也是確保設計滿足所有規格要求的關鍵環節。這包括功能驗證、時序驗證、功耗驗證等,使用各種仿真工具和測試平臺來模擬芯片在各種工作條件下的行為,確保設計沒有缺陷。 在整個設計流程中,每個階段都需要嚴格的審查和反復的迭代。這是因為芯片設計的復雜性要求每一個環節都不能有差錯,任何小的疏忽都可能導致終產品的性能不達標或無法滿足成本效益。設計師們必須不斷地回顧和優化設計,以應對技術要求和市場壓力的不斷變化。高效的芯片架構設計可以平衡計算力、存儲和能耗,滿足多元化的市場需求。江蘇28nm芯片性能

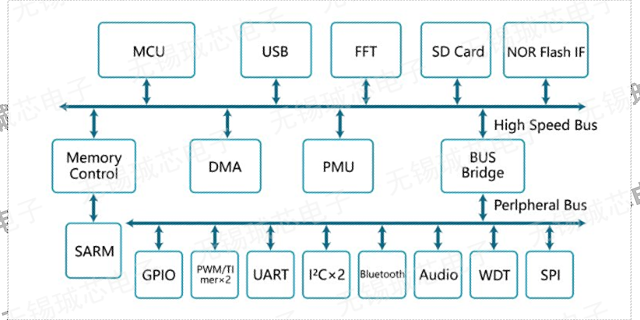

MCU芯片憑借其靈活性和可編程性,在物聯網、智能家居等領域大放異彩。北京網絡芯片后端設計

功耗優化是芯片設計中的另一個重要方面,尤其是在移動設備和高性能計算領域。隨著技術的發展,用戶對設備的性能和續航能力有著更高的要求,這就需要設計師們在保證性能的同時,盡可能降低功耗。功耗優化可以從多個層面進行。在電路設計層面,可以通過使用低功耗的邏輯門和電路結構來減少靜態和動態功耗。在系統層面,可以通過動態電壓頻率調整(DVFS)技術,根據負載情況動態調整電源電壓和時鐘頻率,以達到節能的目的。此外,設計師們還會使用電源門控技術,將不活躍的電路部分斷電,以減少漏電流。在軟件層面,可以通過優化算法和任務調度,減少對處理器的依賴,從而降低整體功耗。功耗優化是一個系統工程,需要硬件和軟件的緊密配合。設計師們需要在設計初期就考慮到功耗問題,并在整個設計過程中不斷優化和調整。北京網絡芯片后端設計